Document Number: MC33660 Rev 5.0, 10/2013

**√**RoHS

# ISO K Line Serial Link Interface

The 33660 is a serial link bus interface device designed to provide bi-directional half-duplex communication interfacing in automotive diagnostic applications. It is designed to interface between the vehicle's on-board microcontroller, and systems off-board the vehicle via the special ISO K line. The 33660 is designed to meet the Diagnostic Systems ISO9141 specification. The device's K line bus driver's output is fully protected against bus shorts and overtemperature conditions.

The 33660 derives its robustness to temperature and voltage extremes by being built on a SMARTMOS process, incorporating CMOS logic, bipolar/MOS analog circuitry, and DMOS power FETs. Although the 33660 was principally designed for automotive applications, it is suited for other serial communication applications. It is parametrically specified over an ambient temperature range of -40 °C  $\leq$  T $_{A}$   $\leq$  125 °C and 8.0 V  $\leq$  V $_{BB}$   $\leq$  18 V supply. The economical SO-8 surface-mount plastic package makes the 33660 very cost effective.

#### **Features**

- Operates over wide supply voltage of 8.0 to 18 V

- · Operating temperature of -40 to 125 °C

- · Interfaces directly to standard CMOS microprocessors

- ISO K line pin protected against shorts to battery

- · Thermal shutdown with hysteresis

- · ISO K line pin capable of high currents

- ISO K line can be driven with up to 10 nF of parasitic capacitance

- 8.0 kV ESD protection attainable with few additional components

- Standby mode: no V<sub>BAT</sub> current drain with V<sub>DD</sub> at 5.0 V

- Low current drain during operation with V<sub>DD</sub> at 5.0 V

## 33660

#### **ISO9141 PHYSICAL INTERFACE**

EF SUFFIX (PB-FREE) 98ASB42564B 8-PIN SOICN

| ORDERING INFORMATION                                          |                                        |         |  |  |

|---------------------------------------------------------------|----------------------------------------|---------|--|--|

| <b>Device</b><br>(For tape and reel orders, add an R2 suffix) | Temperature<br>Range (T <sub>A</sub> ) | Package |  |  |

| MC33660EF                                                     | -40 to 125 °C                          | 8-SOICN |  |  |

| MC33660BEF                                                    | -40 to 125 C                           | 0-301CN |  |  |

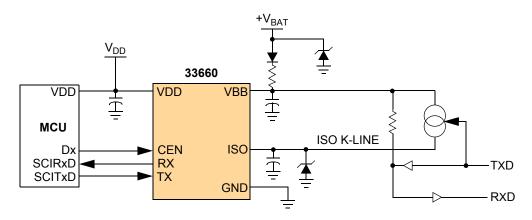

Figure 1. 33660 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice. © Freescale Semiconductor, Inc., 2011-2013. All rights reserved.

# **DEVICE VARIATIONS**

**Table 1. Device Variations**

| Parameter                                                               | Symbol              | Condition                                                                    | 33660 | 33660B <sup>(1)</sup> |

|-------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------|-------|-----------------------|

| VBB Load Dump Peak Voltage (in accordance with ISO 7637-2 & ISO 7637-3) | V <sub>BB(5a)</sub> | Pulse 5a<br>470 ohm series resistor<br>and 100 nF capacitor to<br>GND on VBB | -     | 82 V                  |

|                                                                         | V <sub>BB(5b)</sub> | Pulse 5b<br>470 ohm series resistor<br>and 100 nF capacitor to<br>GND on VBB | 45 V  | 45 V                  |

| Module Level ESD (Air Discharge, Powered) (6)                           | V <sub>ESD4</sub>   | 33 V zener diode and<br>470 pF capacitor to<br>GND on ISO                    | -     | ±25000 V              |

## Notes

1. Recommended for all new designs

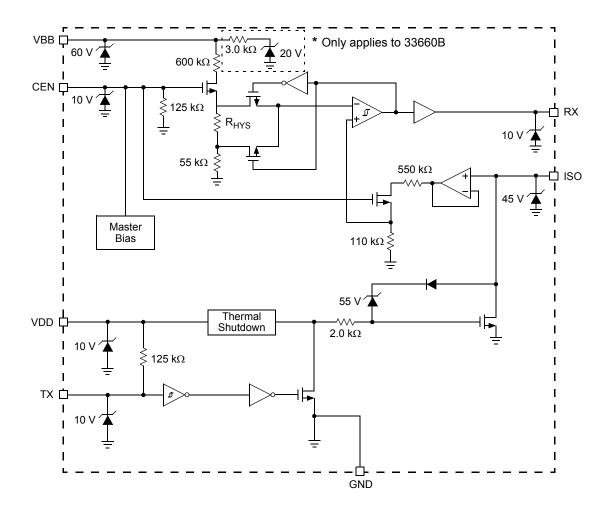

## INTERNAL BLOCK DIAGRAM

Figure 2. 33660 Simplified Internal Block Diagram

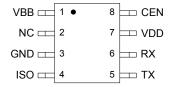

## **PIN CONNECTIONS**

Figure 3. 33660 Pin Connections

Table 2. 33660 Pin Definitions

| Pin Number | Pin Name | Definition                                                          |

|------------|----------|---------------------------------------------------------------------|

| 1          | VBB      | Battery power through external resistor and diode.                  |

| 2          | NC       | Not to be connected. (2)                                            |

| 3          | GND      | Common signal and power return.                                     |

| 4          | ISO      | Bus connection.                                                     |

| 5          | TX       | Logic level input for data to be transmitted on the bus.            |

| 6          | RX       | Logic output of data received on the bus.                           |

| 7          | VDD      | Logic power source input.                                           |

| 8          | CEN      | Chip enable. Logic "1" for active state. Logic "0" for sleep state. |

## Notes

2. NC pins should not have any connections made to them. NC pins are not guaranteed to be open circuits.

## **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Rating                                                                  | Symbol              | Value       | Unit |  |

|-------------------------------------------------------------------------|---------------------|-------------|------|--|

| VDD DC Supply Voltage                                                   | $V_{DD}$            | -0.3 to 7.0 | V    |  |

| VBB Load Dump Peak Voltage (in accordance with ISO 7637-2 & ISO 7637-3) |                     |             | V    |  |

| Pulse 5a - 33660B only                                                  | V <sub>BB(5a)</sub> | 82          |      |  |

| Pulse 5b                                                                | V <sub>BB(5b)</sub> | 45          |      |  |

| SO Pin Load Dump Peak Voltage (3)                                       | V <sub>ISO</sub>    | 40          | V    |  |

| ESD Voltage <sup>(4)</sup>                                              |                     |             | V    |  |

| Human Body Model <sup>(5)</sup>                                         | V <sub>ESD1</sub>   | ±2000       |      |  |

| Machine Model (5)                                                       | V <sub>ESD2</sub>   |             |      |  |

| 33660                                                                   |                     | ±150        |      |  |

| 33660B                                                                  |                     | ±200        |      |  |

| Charge Device Model <sup>(5)</sup>                                      |                     |             |      |  |

| Corner Pins                                                             | V <sub>ESD3-1</sub> | ±750        |      |  |

| All other Pins                                                          | V <sub>ESD3-2</sub> | ±500        |      |  |

| Module Level ESD (Air Discharge, Powered) (6)                           |                     |             |      |  |

| 33660B only                                                             | V <sub>ESD4</sub>   | ±25000      |      |  |

| ISO pin with 33 V zener diode and 470 pF capacitor to GND -             |                     |             |      |  |

| ISO Clamp Energy <sup>(7)</sup>                                         | E <sub>CLAMP</sub>  | 10          | mJ   |  |

| Storage Temperature                                                     | T <sub>STG</sub>    | -55 to +150 | °C   |  |

| Operating Case Temperature                                              | T <sub>C</sub>      | -40 to +125 | °C   |  |

| Operating Junction Temperature                                          | T <sub>J</sub>      | -40 to +150 | °C   |  |

| Power Dissipation T <sub>A</sub> = 25 °C                                | P <sub>D</sub>      | 100         | mW   |  |

| Peak Package Reflow Temperature During Reflow (8), (9)                  | T <sub>PPRT</sub>   | Note 9.     | °C   |  |

| Thermal Resistance: Junction-to-Ambient                                 | $R_{	heta JA}$      | 150         | °C/W |  |

## Notes

- 3. Device will survive double battery jump start conditions in typical applications for 10 minutes duration, but is not guaranteed to remain within specified parametric limits during this duration.

- 4. ESD data available upon request.

- 5. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ), ESD3 testing is performed in accordance with the Charge Device Model ( $C_{ZAP}$  = 4.0 pF).

- 6. ESD4 testing is performed in accordance with ISO 10605 ESD model (C = 330 pF, R = 2.0 kΩ). ESD discharges start at ±5.0 kV and go up to ±25 kV in increments of 5.0 kV. There are two positions for discharges: 8.0 cm cable from ISO connector, 85 cm cable from ISO connector. There are 10 ESD discharges per voltage at each cable position at a minimum of 1.0 s intervals. Remaining charge is not bled off after every discharge.

- 7. Nonrepetitive clamping capability at 25 °C.

- 8. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 9. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

33660

## STATIC ELECTRICAL CHARACTERISTICS

**Table 4. Static Electrical Characteristics**

Characteristics noted under conditions of 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, 8.0 V  $\leq$  V<sub>BB</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>C</sub>  $\leq$  125 °C, unless otherwise noted.

| Characteristic                                                               | Symbol               | Min                   | Тур | Max                   | Unit |

|------------------------------------------------------------------------------|----------------------|-----------------------|-----|-----------------------|------|

| POWER AND CONTROL                                                            | •                    | •                     |     |                       | I.   |

| V <sub>DD</sub> Sleep State Current                                          | I <sub>DD(SS)</sub>  |                       |     |                       | mA   |

| $T_x = 0.8 V_{DD}, CEN = 0.3 V_{DD}$                                         |                      | _                     | _   | 0.1                   |      |

| V <sub>DD</sub> Quiescent Operating Current                                  | I <sub>DD(Q)</sub>   |                       |     |                       | mA   |

| $T_{x} = 0.2 V_{DD}, CEN = 0.7 V_{DD}$                                       |                      | _                     | -   | 1.0                   |      |

| V <sub>BB</sub> Sleep State Current                                          | I <sub>BB(SS)</sub>  |                       |     |                       | μΑ   |

| $V_{BB}$ = 16 V, $T_x$ = 0.8 $V_{DD}$ , CEN = 0.3 $V_{DD}$                   |                      | _                     | -   | 50                    |      |

| V <sub>BB</sub> Quiescent Operating Current                                  | I <sub>BB(Q)</sub>   |                       |     |                       | mA   |

| $T_X = 0.2 V_{DD}, CEN = 0.7 V_{DD}$                                         |                      | _                     | _   | 1.0                   |      |

| Chip Enable                                                                  |                      |                       |     |                       | V    |

| Input High Voltage Threshold (10)                                            | V <sub>IH(CEN)</sub> | 0.7 V <sub>DD</sub>   | _   | _                     |      |

| Input Low Voltage Threshold (11)                                             | $V_{IL(CEN)}$        | _                     | _   | 0.3 V <sub>DD</sub>   |      |

| Chip Enable Pull-down Current (12)                                           | I <sub>PD(CEN)</sub> | 2.0                   | _   | 40                    | μΑ   |

| T <sub>X</sub> Input Low Voltage Threshold                                   | $V_{IL(TX)}$         |                       |     |                       | V    |

| $R_{ISO}$ = 510 $\Omega$ <sup>(13)</sup>                                     |                      | _                     | _   | 0.3 x V <sub>DD</sub> |      |

| T <sub>X</sub> Input High Voltage Threshold                                  | V <sub>IH(TX)</sub>  |                       |     |                       | V    |

| $R_{ISO}$ = 510 $\Omega$ <sup>(14)</sup>                                     |                      | 0.7 x V <sub>DD</sub> | _   | _                     |      |

| T <sub>X</sub> Pull-up Current <sup>(15)</sup>                               | I <sub>PU(TX)</sub>  | -40                   | -   | -2.0                  | μA   |

| R <sub>X</sub> Output Low Voltage Threshold                                  | V <sub>OL(RX)</sub>  |                       |     |                       | V    |

| $R_{ISO}$ = 510 $\Omega$ , $T_X$ = 0.2 $V_{DD}$ , $R_X$ Sinking 1.0 mA       |                      | _                     | _   | 0.2 V <sub>DD</sub>   |      |

| R <sub>X</sub> Output High Voltage Threshold                                 | V <sub>OH(RX)</sub>  |                       |     |                       | V    |

| $R_{ISO}$ = 510 $\Omega$ , $T_X$ = 0.8 $V_{DD}$ , $R_X$ Sourcing 250 $\mu A$ |                      | 0.8 V <sub>DD</sub>   | _   | _                     |      |

| Thermal Shutdown (16)                                                        | T <sub>LIM</sub>     | 150                   | 170 | _                     | °C   |

## Notes

- 10. When  $I_{BB}$  transitions to >100  $\mu$ A.

- 11. When  $I_{BB}$  transitions to <100  $\mu A$ .

- 12. Enable pin has an internal current pull-down. Pull-down current is measured with CEN pin at  $0.3 \text{ V}_{DD}$ .

- 13. Measured by ramping  $T_X$  down from 0.8  $V_{DD}$  and noting  $T_X$  value at which ISO falls below 0.2  $V_{BB}$ .

- 14. Measured by ramping  $T_X$  up from 0.2  $V_{DD}$  and noting the value at which ISO rises above 0.9  $V_{BB}$ .

- 15.  $T_x$  pin has internal current pull-up. Pull-up current is measured with  $T_X$  pin at 0.7  $V_{DD}$ .

- 16. Thermal Shutdown performance  $(T_{LIM})$  is guaranteed by design, but not production tested.

## **Table 3. Static Electrical Characteristics (Continued)**

Characteristics noted under conditions of 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, 8.0 V  $\leq$  V<sub>BB</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>C</sub>  $\leq$  125°C, unless otherwise noted.

| Characteristic                                                                          | Symbol                | Min                    | Тур | Max                   | Unit |

|-----------------------------------------------------------------------------------------|-----------------------|------------------------|-----|-----------------------|------|

| ISO I/O                                                                                 | 1                     |                        |     |                       |      |

| Input Low Voltage Threshold                                                             | V <sub>IL(ISO)</sub>  |                        |     |                       | V    |

| $R_{ISO}$ = 510 $\Omega$ , $T_X$ = 0.8 $V_{DD}$                                         |                       | _                      | -   | 0.4 x V <sub>BB</sub> |      |

| Input High Voltage Threshold                                                            | V <sub>IH(ISO)</sub>  |                        |     |                       | V    |

| $R_{ISO}$ = 510 $\Omega$ , $T_X$ = 0.8 $V_{DD}$                                         |                       | 0.7 x V <sub>BB</sub>  | -   | _                     |      |

| Input Voltage Hysteresis                                                                | V <sub>HYS(ISO)</sub> | 0.05 x V <sub>BB</sub> | _   | 0.1 x V <sub>BB</sub> | V    |

| Internal Pull-up Current                                                                | I <sub>PU(ISO)</sub>  |                        |     |                       | μA   |

| $R_{ISO}$ = $\infty \Omega$ , $T_X$ = 0.8 $V_{DD}$ , $V_{ISO}$ = 9.0 V, $V_{BB}$ = 18 V |                       | -5.0                   | -   | -140                  |      |

| Short-circuit Current Limit                                                             | I <sub>SC(ISO)</sub>  |                        |     |                       | mA   |

| $R_{ISO}$ = 0 $\Omega$ , $T_X$ = 0.4 $V_{DD}$ , $V_{ISO}$ = $V_{BB}$                    |                       | 50                     | -   | 200                   |      |

| Output Low Voltage                                                                      | V <sub>OL(ISO)</sub>  |                        |     |                       | V    |

| $R_{ISO}$ = 510 $\Omega$ , $T_X$ = 0.2 $V_{DD}$                                         |                       | -                      | -   | 0.1 x V <sub>BB</sub> |      |

| Output High Voltage                                                                     | V <sub>OH(ISO)</sub>  |                        |     |                       | V    |

| $R_{ISO}$ = $\infty \Omega$ , $T_X$ = 0.8 $V_{DD}$                                      |                       | 0.95 x V <sub>BB</sub> | -   | _                     |      |

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

## **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions of 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, 8.0 V  $\leq$  V<sub>BB</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>C</sub>  $\leq$  125 °C, unless otherwise noted.

| Characteristic                                                             | Symbol                 | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| Fall Time (17)                                                             | t <sub>FALL(ISO)</sub> |     |     |     | μs   |

| $R_{ISO}$ = 510 $\Omega$ to $V_{BB}$ , $C_{ISO}$ = 10 nF to Ground         |                        | -   | _   | 2.0 |      |

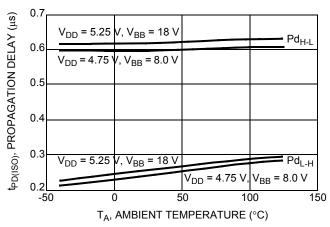

| ISO Propagation Delay (18)                                                 | t <sub>PD(ISO)</sub>   |     |     |     | μs   |

| High to Low: $R_{ISO} = 510 \Omega$ , $C_{ISO} = 500 pF$ (19)              |                        | _   | _   | 2.0 |      |

| Low to High: $R_{ISO}$ = 510 $\Omega$ , $C_{ISO}$ = 500 pF <sup>(20)</sup> |                        | 1   | I   | 2.0 |      |

## Notes

- 17. Time required ISO voltage to transition from 0.8  $V_{BB}$  to 0.2  $V_{BB}$ .

- 18. Changes in the value of  $C_{ISO}$  affect the rise and fall time but have minimal effect on Propagation Delay.

- 19. Step  $T_X$  voltage from 0.8  $V_{DD}$  to 0.2  $V_{DD}$ . Time measured from  $V_{IH(Tx)}$  until  $V_{ISO}$  reaches 0.3  $V_{BB}$ .

- 20. Step  $T_X$  voltage from 0.2  $V_{DD}$  to 0.8  $V_{DD}$ . Time measured from  $V_{IL(Tx)}$  until  $V_{ISO}$  reaches 0.7  $V_{BB}$ .

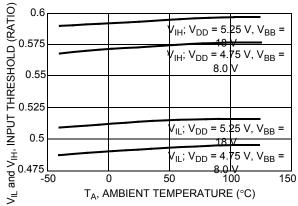

## **ELECTRICAL PERFORMANCE CURVES**

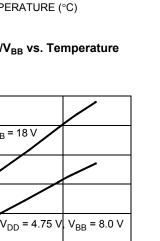

Figure 4. ISO Input Threshold/ $V_{BB}$  vs. Temperature

V<sub>DD</sub> = 5.25 V, V<sub>BB</sub> = 18 V

0.95

0.9

0.85

0.8

0.75

0.7

0.65

-50

$t_{\text{fall(ISO)}}$ , ISO FALL TIME ( $\mu s$ )

150

100

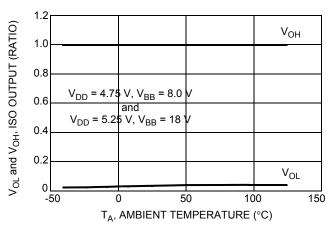

Figure 5. ISO Output/V<sub>BB</sub> vs. Temperature

50

T<sub>A</sub>, AMBIENT TEMPERATURE (°C)

Figure 6. ISO Fall Time vs. Temperature

Figure 7. ISO Propagation Delay vs. Temperature

## TYPICAL APPLICATIONS

## INTRODUCTION

The 33660 is a serial link bus interface device conforming to the ISO 9141 physical bus specification. The device is designed for automotive environment usage, compliant with On-board Diagnostics (OBD) requirements set forth by the California Air Resources Board (CARB) using the ISO K line. The device does not incorporate an ISO L line. It provides bidirectional half-duplex communications interfacing from a

microcontroller to the communication bus. The 33660 incorporates circuitry to interface the digital translations from 5.0 V microcontroller logic levels to battery level logic, and from battery level logic to 5.0 V logic levels. The 33660 is built using Freescale Semiconductor's SMARTMOS process and is packaged in an 8-pin plastic SOIC.

#### **FUNCTIONAL DESCRIPTION**

The 33660 transforms 5.0 V microcontroller logic signals to battery level logic signals and visa versa. The maximum data rate is set by the rise and fall time. The fall time is set by the output driver. The rise time is set by the bus capacitance and the pull-up resistors on the bus. The fall time of the 33660 allows data rates up to 150 kbps using a 30 percent maximum bit time transition value. The serial link interface will remain fully functional over a battery voltage range of 6.0 to 18 V. The device is parametrically specified over a dynamic  $V_{\rm BB}$  voltage range of 8.0 to 18 V.

Required input levels from the microcontroller are ratiometric with the  $V_{DD}$  voltage normally used to power the microcontroller. This enhances the 33660's ability to remain in harmony with the  $R_X$  and  $T_X$  control input signals of the microcontroller. The  $R_X$  and  $T_X$  control inputs are compatible with standard 5.0 V CMOS circuitry. For fault tolerant purposes the  $T_X$  input from the microcontroller has an internal

passive pull-up to  $V_{DD}$ , while the CEN input has an internal passive pull-down to ground.

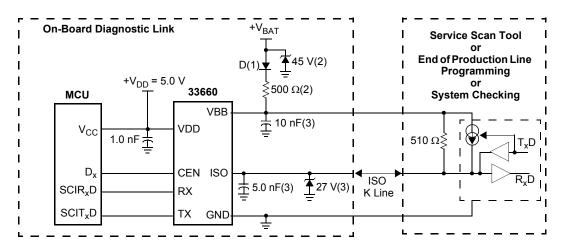

A pull-up to battery is internally provided as well as an active data pull-down. The internal active pull-down is current-limit protected against shorts to battery, and further protected by thermal shutdown. Typical applications have reverse battery protection by the incorporation of an external 510  $\Omega$  pull-up resistor and a diode to battery.

Reverse battery protection of the device is provided by the use of a reverse battery blocking diode (See "D" in the Typical Application Diagram on page 10). Battery line transient protection of the device is provided for by using a 45 V zener and a 500  $\Omega$  resistor connected to the  $V_{BB}$  source, as shown in the same diagram. Device ESD protection from the communication lines exiting the module is through the use of the capacitor connected to the  $V_{BB}$  device pin, and the capacitor used in conjunction with the 27 V zener connected to the ISO pin.

Components necessary for Reverse Battery (1), Overvoltage Transient (2), and 8.0 kV ESD Protection (3) in a metal module case.

Figure 8. Typical Application Diagram

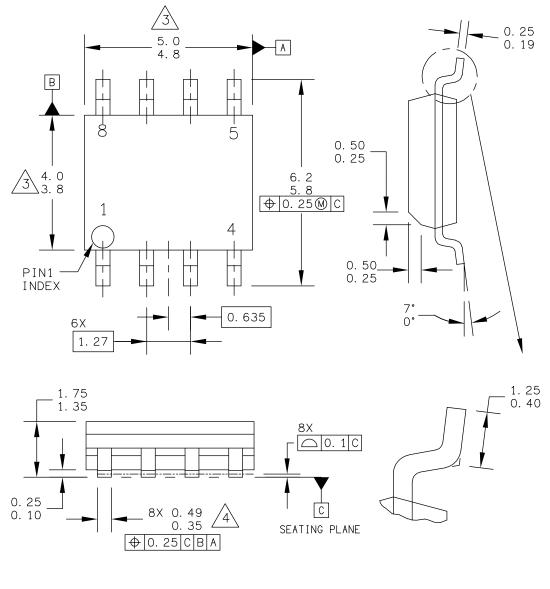

## **PACKAGING**

## **PACKAGE DIMENSIONS**

For the most current package revision, visit <u>www.freescale.com</u> and perform a keyword search using the "98A" listed below.

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECHANICA |        | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------------------|--------|--------------|------------------|-------------|

| TITLE:                                                           |        | DOCUMENT NO  | ): 98ASB42564B   | REV: V      |

| 8LD SOIC NARROW                                                  | / BODY | CASE NUMBER  | 2: 751–07        | 20 NOV 2007 |

|                                                                  |        | STANDARD: JE | DEC MS-012AA     |             |

EF SUFFIX (PB-FREE) 8-PIN 98ASB42564B REV. V

33660

# PACKAGING PACKAGE DIMENSIONS

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECH |        | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|-------------------------------------------------------------|--------|--------------|------------------|-------------|

| TITLE:                                                      |        | DOCUMENT NO  | ): 98ASB42564B   | REV: V      |

| 8LD SOIC NARROV                                             | W BODY | CASE NUMBER  | R: 751–07        | 20 NOV 2007 |

|                                                             |        | STANDARD: JE | IDEC MS-012AA    |             |

EF SUFFIX (PB-FREE) 8-PIN 98ASB42564B REV. V

# **REVISION HISTORY**

| REVISION | DATE    | DESCRIPTION OF CHANGES                                                                                                                                                                                                                                                                                                                                                                     |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 1/2011  | Initial release                                                                                                                                                                                                                                                                                                                                                                            |

| 2.0      | 9/2011  | Adjusted format to meet current compliance standards. No data was altered.                                                                                                                                                                                                                                                                                                                 |

| 3.0      | 10/2011 | Updated the PC part number to MC.                                                                                                                                                                                                                                                                                                                                                          |

| 4.0      | 2/2013  | <ul> <li>Added PC33660BEF to the ordering information</li> <li>Redefined VBB Load Dump Peak Voltage (in accordance with ISO 7637-2 &amp; ISO 7637-3) for the 33660B</li> <li>Added Module Level ESD (Air Discharge, Powered) (6) for the 33660B</li> <li>Added note (6)</li> <li>Increased ESD structure voltage for 33660B, and added bleed-off circuit on VBB pin in Figure 2</li> </ul> |

| 5.0      | 10/2013 | Clarified machine model limits for MC33660 and MC33660B page 5                                                                                                                                                                                                                                                                                                                             |

#### How to Reach Us:

Home Page: freescale.com

Web Support:

freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions..

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. SMARTMOS is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

Document Number: MC33660

Rev 5.0 10/2013